# MARVELL® Prestera® 98DX4310 Multi-Layer Ethernet Switch

A new generation of highly-integrated packet processors for high-end Enterprise multi-Gig access

#### **PRODUCT OVERVIEW**

The Prestera® 98DX4310 multi-layer Ethernet switch device is a new generation of highly-integrated packet processors. It is built for premium enterprise and campus access multi-Gig applications where 1/2.5/5GbE is required, such as: Campus LAN Access Switch, Wi-Fi 802.11ac Wave2 Access Point Aggregation.

The 98DX4310 supports advanced table scale and feature set for the high-end access switch platform migrating to 2.5GbE and 5GbE access ports. The device supports 25GbE uplinks to the network backbone and dedicated stacking ports.

The 98DX4310 supports advanced telemetry and analytics capabilities for network visibility and troubleshooting.

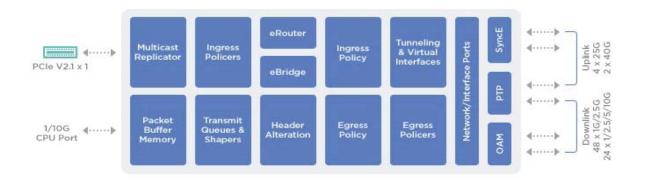

#### **BLOCK DIAGRAM**

Marvell 98DX4310

### **KEY FEATURES AND BENEFITS**

| FEATURES                   | BENEFITS                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port Interface             | <ul> <li>48 ports of 1/2.5 GbE or 24 ports of 1/2.5/5/10 GbE</li> <li>4 ports of 25 GbE or 2 ports of 40 GbE</li> <li>2 stacking ports of 100GbE</li> <li>1 port of 10 GbE Port for CPU management</li> </ul>                                                                                                                                                                                         |

| Management I/O             | PCle interface Gen 2.1 x1  1 Ethernet port of up to 10GbE for control traffic to the CPU                                                                                                                                                                                                                                                                                                              |

| Highly Integrated          | <ul> <li>Large forwarding tables</li> <li>Large packet buffer memory</li> <li>Shared TCAMs resources with Flexible TCAM sizes</li> <li>High-speed SERDES</li> </ul>                                                                                                                                                                                                                                   |

| Telemetry and Analytics    | To facilitate efficient network self-healing and troubleshooting  Extensive counters across most processing engines for advanced telemetry and analytics functionality                                                                                                                                                                                                                                |

| Fowarding Engines          | <ul> <li>Layer-2 Wire-Speed Switching engine with large MAC table</li> <li>Layer-3 Wire-Speed Routing engine with large LPM table</li> <li>CAPWAP overlay support</li> <li>Virtualization - IEEE 802.1Qbg EVB, 802.1BR Port Extender</li> <li>Virtual overlay networking - NVGRE, VXLAN-GPE, GENEVE, SPB, TRILL, GRE</li> <li>NFV Service Function Chaining - Network Service Header (NSH)</li> </ul> |

| Quality of Service         | <ul> <li>1K QoS Profile to flexibly assign a packet traffic class, drop precedence, and packet CoS marking</li> <li>8 priority queues per physical port, with scheduling support for Strict Priority and Shaped Deficit Weighted Round-Robin (SDWRR)</li> <li>Ingress/Egress Policers compliant with MEF 10.2 Single/Two Rate 3-Color Marking, and MEF 10.3 bandwidth sharing</li> </ul>              |

| Optimal HW Design          | <ul> <li>Two power rails: 1v, 1.8v</li> <li>Optimal power consumption in its category</li> <li>Small footprint</li> <li>Single clock source</li> <li>8 layer PCB with 25G Interface</li> <li>FR4 for 10G uplink and stacking</li> </ul>                                                                                                                                                               |

| Software and Compatibility | SW compatibility to 98DX42xx, 98DX83xx, 98DX84xx, 98DX85xx     Stacking compatibility to 98DX84xx, 98DX85xx, and 98EX55xx-aggregation switches for campus 2-tier deployments                                                                                                                                                                                                                          |

## **TARGET APPLICATIONS**

- Enterprise Campus high-end feature rich Access switch for multi-Gig access connecting to 25GbE campus networks

- Wi-Fi 802.11ac Wave2 Access Point Aggregation

To deliver the data infrastructure technology that connects the world, we're building solutions on the most powerful foundation: our partnerships with our customers. Trusted by the world's leading technology companies for 25 years, we move, store, process and secure the world's data with semiconductor solutions designed for our customers' current needs and future ambitions. Through a process of deep collaboration and transparency, we're ultimately changing the way tomorrow's enterprise, cloud, automotive, and carrier architectures transform—for the better.

$Copyright @\ 2022\ Marvell.\ All\ rights\ reserved.\ Marvell\ and\ the\ Marvell\ logo\ are\ trademarks\ of\ Marvell\ or\ its\ affiliates.\ Please\ visit\ \underline{www.marvell.com}\ for\ a\ complete\ list\ of\ Marvell\ trademarks.\ Other\ names\ and\ brands\ may\ be\ claimed\ as\ the\ property\ of\ others.$