# Prestera® 8500C Series Switches

12.8 Tbps Ethernet switch for enterprise campus aggregation P/N 98CX85xx

#### **Overview**

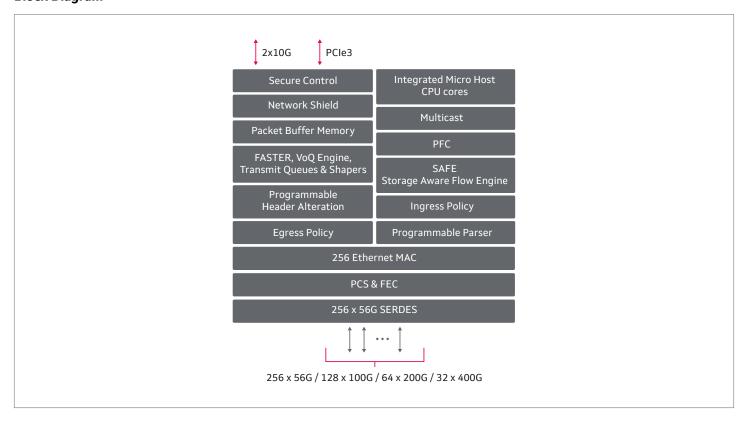

The Marvell® Prestera® 8500C series (P/N 98CX85xx) are fully integrated Ethernet switch ASICs optimized for high-bandwidth aggregation/distribution-layer applications in the enterprise. The 12.8 Tbps CX8580 includes 256 high-speed 56G PAM4 SerDes enabling 32 400G Ethernet MAC interfaces.

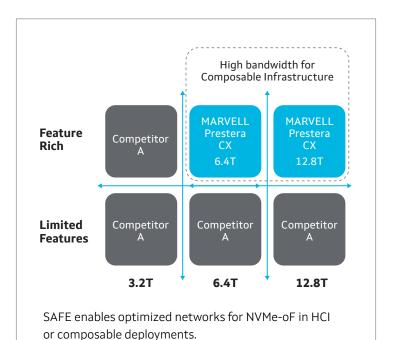

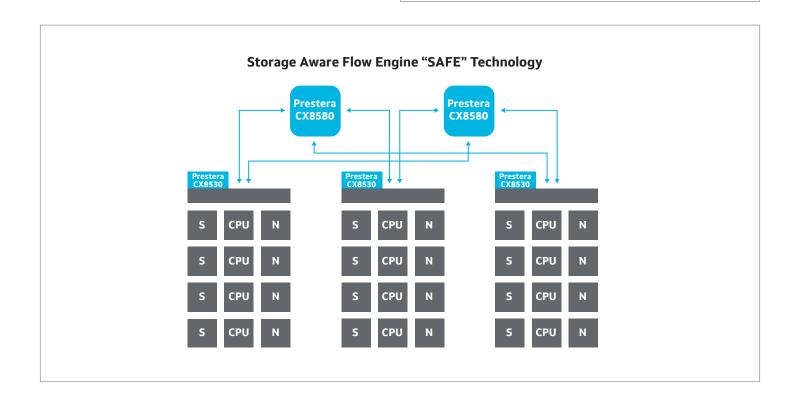

The Prestera® 8500C series devices include Storage Aware Flow Engine (SAFE) technology which enables visibility in to data center deployments that utilize HCI or composable infrastructure enabled by storage disaggregation platforms running NVMe-oF. SAFE enables telemetry at the RDMA flow level enabling operators to pin point aggressor hosts or congested disks and guarantee service levels and fairness amongst hosts and storage resources across the network.

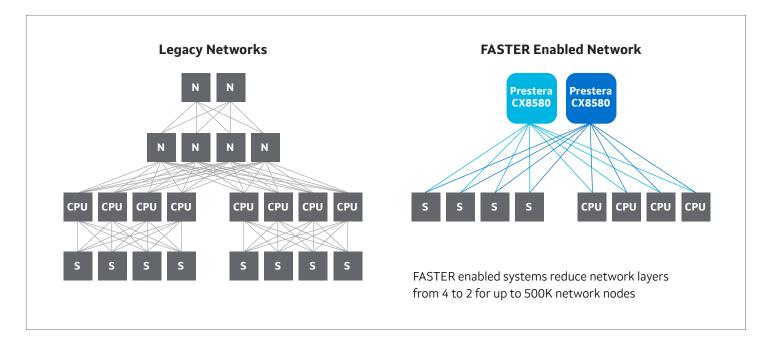

The Prestera CX device also includes Forwarding Architecture using Slices of Terabit Ethernet Routers (FASTER) technology that enables high radix systems to be built with end-to-end QoS at latency, power and cost at greater than 30% savings over standard ethernet CLOS architectures. FASTER enables reduction of network layers for scale out deployments through it 1,000 port radix capability. The result is a solution with high port radix enabling a reduction of network layers translating to lower CO with a huge savings in network equipment, wiring and optics.

Combining the SAFE and FASTER technology, the newest Prestera CX family provides the ideal solution for the roll out of edge data center deployments where composable infrastructure provides the flexibility for adapting to the wide range of applications being deployed at the edge based on the 5G and IOT build out. With the edge data center network being collapsed into a single layer and the enhanced visibility of the storage flows in the network, the Prestera CX enables the most efficient edge data center design with the highest performance, lowest latency and best ROI for the equipment deployed in these locations.

### **Block Diagram**

## **Key Features**

| Packet Processor     | <ul> <li>9th generation ethernet switch pipeline deployed in enterprise, service provider and data center networks</li> <li>Leveraging stable 16nm high volume process node enabling quick TTM for customers</li> </ul>                                                                      |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Speed I/O       | <ul> <li>256 of the leading edge 56G PAM4 LR SerDes supporting DAC or optical interconnects</li> <li>Fully compliant ethernet MAC interfaces to the latest IEEE standard for 1G through 400G rates</li> </ul>                                                                                |

| Traffic Management   | <ul> <li>8K queues with 3 level H-QoS and VoQ support for 1K ports</li> <li>Support for elephant flow detection and packet prioritization using advanced proactive hardware probes that can predict congestion before the event occurs</li> </ul>                                            |

| Forwarding Resources | <ul> <li>Large shared pool of memory dynamically allocated between forwarding engines with &gt;2x capacity of currently available solutions</li> <li>Support for up to 16K ECMP path scale with congestion aware load balancing or DLB with hardware to prevent 0o0 within a flow</li> </ul> |

| Buffer Resources     | <ul> <li>Global Shared packet buffer with dynamic buffer absorption and enhanced micro-burst support</li> <li>Fine grain buffer segmentation provides 2x packet capacity over available solutions in the market</li> </ul>                                                                   |

| Flow Awareness       | <ul> <li>Multi-lookup flow engine capable of using both TCAM and SRAM for lookups on more than 500Kflows</li> <li>RoCEv2 awareness provides flow level diagnostics to identify and resolve network congestion</li> </ul>                                                                     |

# **Target Applications**

Enterprise network fixed and modular aggregation/ distribution

#### **Part Number Matrix**

| Part Number | Bandwidth | I/O Configuration |

|-------------|-----------|-------------------|

| 98CX8580    | 12.8Tbps  | 256 x 56G I/O     |

| 98CX8550    | 8Tbps     | 160 x 56G I/O     |

| 98CX8542    | 6.4Tbps   | 256 x 28G I/O     |

| 98CX8540    | 6.4Tbps   | 128 x 56G I/O     |

| 98CX8530    | 4Tbps     | 80 x 56G I/O      |

| 98CX8522    | 3.2Tbps   | 128 x 28G I/O     |

| 98CX8520    | 3.2Tbps   | 64 x 56G I/O      |

To deliver the data infrastructure technology that connects the world, we're building solutions on the most powerful foundation: our partnerships with our customers. Trusted by the world's leading technology companies over 25 years, we move, store, process and secure the world's data with semiconductor solutions designed for our customers' current needs and future ambitions. Through a process of deep collaboration and transparency, we're ultimately changing the way tomorrow's enterprise, cloud, automotive, and carrier architectures transform—for the better.

Copyright © 2024 Marvell. All rights reserved. Marvell and the Marvell logo are trademarks of Marvell or its affiliates. Please visit <u>www.marvell.com</u> for a complete list of Marvell trademarks. Other names and brands may be claimed as the property of others.