# **Custom Al Investor Event**

June 17, 2025

# Ashish Saran

SVP, Investor Relations

### Forward-looking statements

Except for statements of historical fact, this presentation contains forward-looking statements (within the meaning of the federal securities laws) including, but not limited to, statements related to market trends and to the company's business and operations, business opportunities, growth strategy and expectations, and financial targets and plans, that involve risks and uncertainties. Words such as "anticipates," "expects," "intends," "plans," "projects," "believes," "seeks," "estimates," "can," "may," "will," "would" and similar expressions identify such forward-looking statements. These statements are not guarantees of results and should not be considered as an indication of future activity or future performance. Actual events or results may differ materially from those described in this presentation due to a number of risks and uncertainties.

For factors that could cause Marvell's results to vary from expectations, please see the risk factors identified in Marvell's Quarterly Report on Form 10-Q for the fiscal quarter ended May 3, 2025, as filed with the SEC on May 30, 2025, and Marvell's Annual Report on Form 10-K for the fiscal year ended February 1, 2025, as filed with the SEC on March 12, 2025, and other factors detailed from time to time in Marvell's filings with the SEC. The forward-looking statements in this presentation speak only as of the date of this presentation and Marvell undertakes no obligation to revise or update publicly any forward-looking statements.

### Non-GAAP financial measures

- During this presentation, we may refer to certain financial measures on a U.S. non-GAAP basis.

- We believe that the presentation of non-GAAP financial measures provides important supplemental information to management and investors regarding financial and business trends relating to our financial condition and results of operations.

- While we use non-GAAP financial measures as a tool to enhance our understanding of certain aspects

of our financial performance, we do not consider these measures to be a substitute for, or superior to,

the information provided by GAAP financial measures.

- A reconciliation in accordance with SEC Regulation G for non-GAAP financial measures is available in the Investor Relations section of our website at https://www.marvell.com.

### Agenda

Matt Murphy

Chairman and Chief Executive Officer

Chris Koopmans

Chief Operating Officer

Nick Kucharewski SVP and GM, Cloud Platform

Sandeep Bharathi

Chief Development Officer

Will Chu SVP and GM, Custom Cloud Solutions

Q&A

# **Custom Al Investor Event**

# **Matt Murphy**

Chairman and Chief Executive Officer

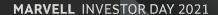

# Cloud-optimized silicon

MARVELL INVESTOR DAY 2021

© 2021 Marvell. All rights reserved.

AFF

AFF

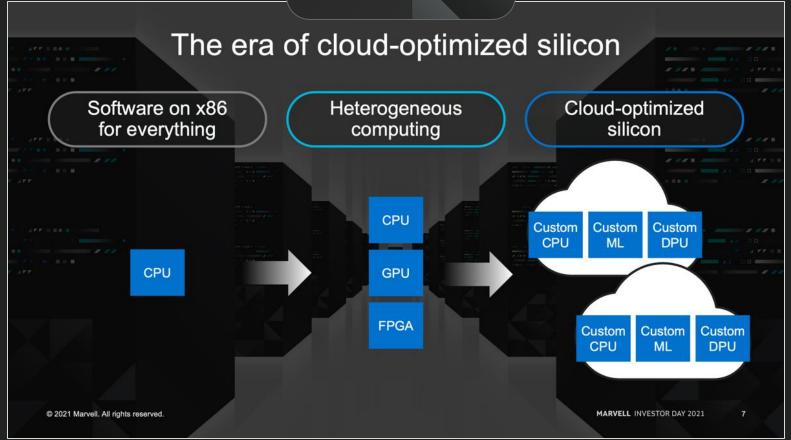

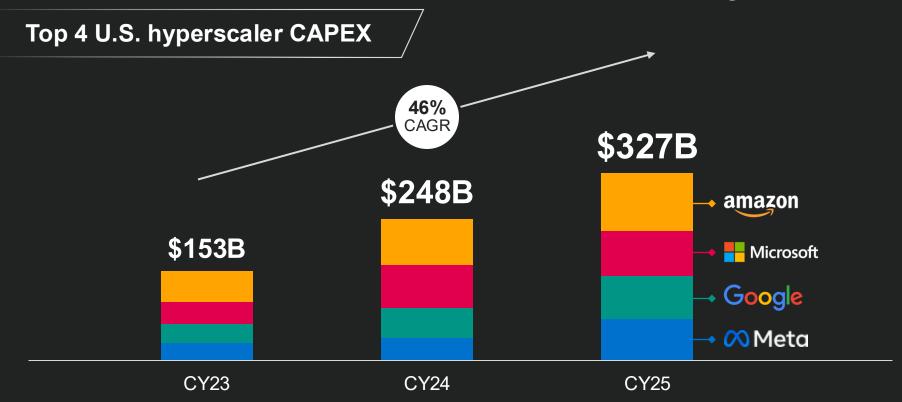

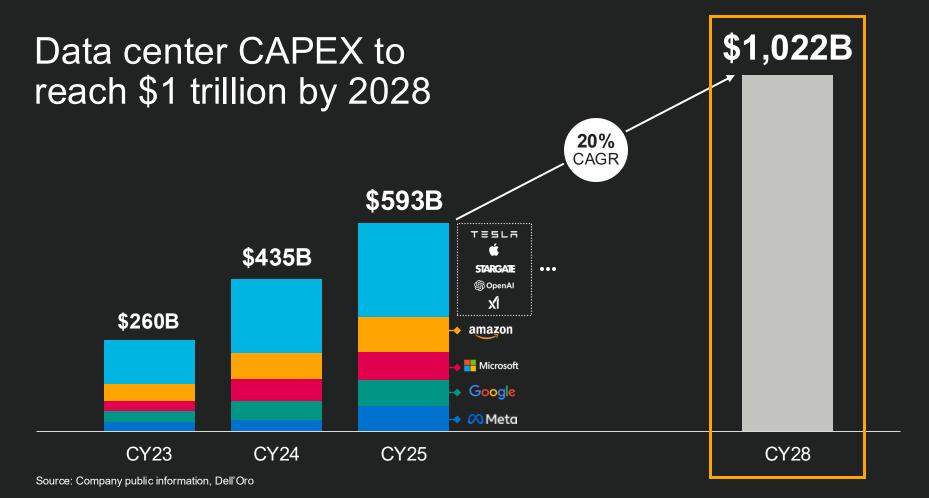

### Al infrastructure buildout drives incredible growth

Source: public information

### Emerging hyperscalers rising fast

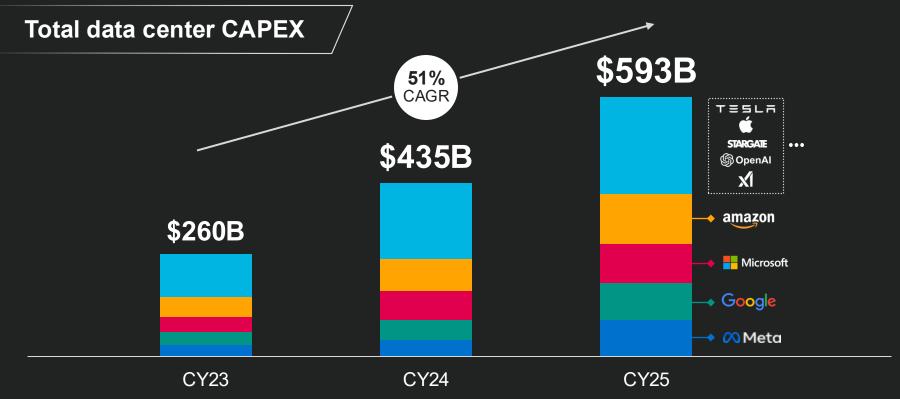

### Al infrastructure buildout drives incredible growth

Source: public information

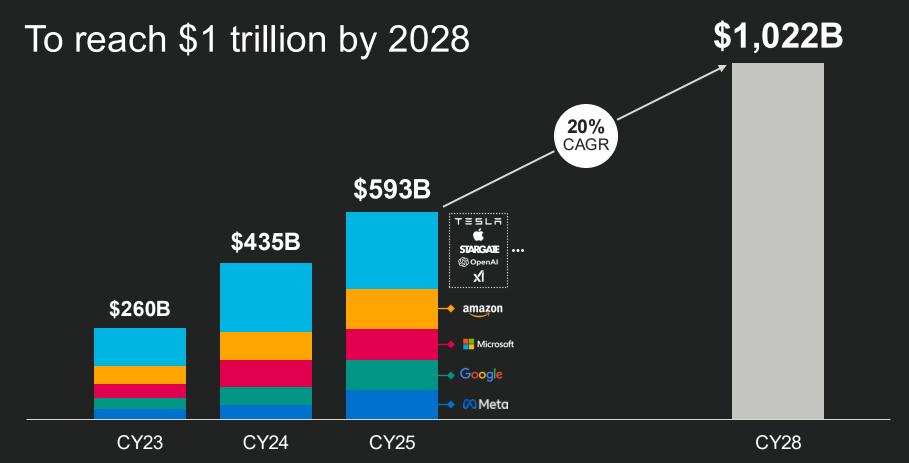

### Al infrastructure buildout drives incredible growth

Source: public information, Dell'Oro

Source: public information, Dell'Oro

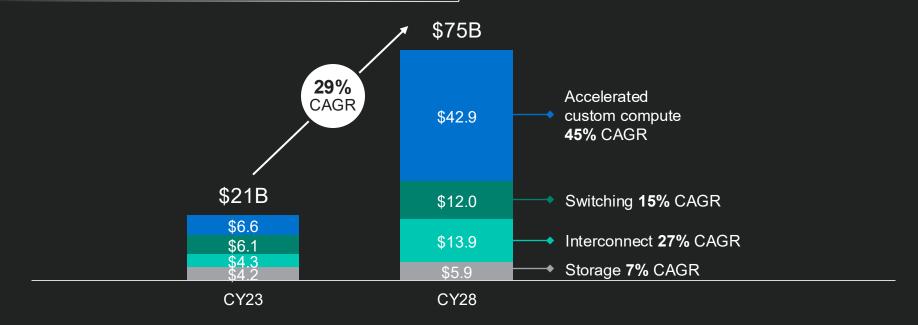

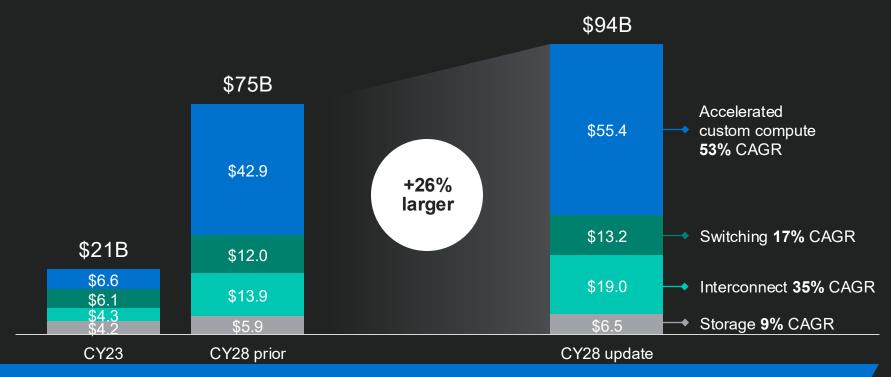

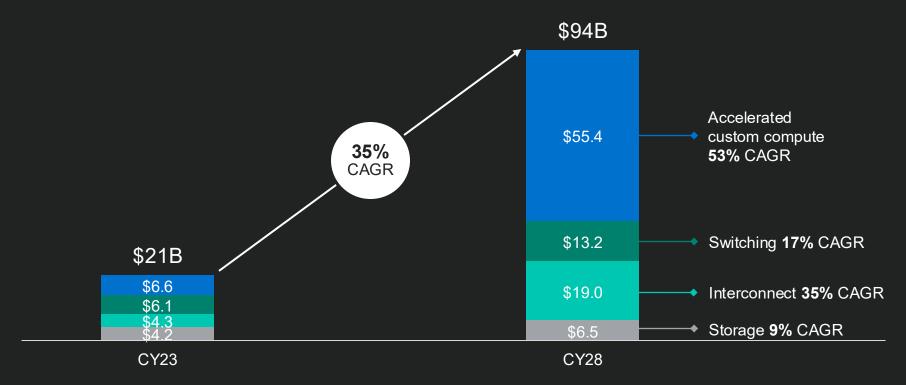

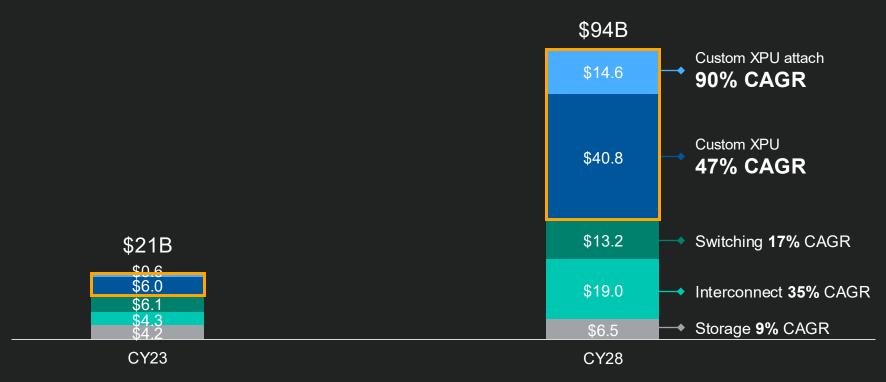

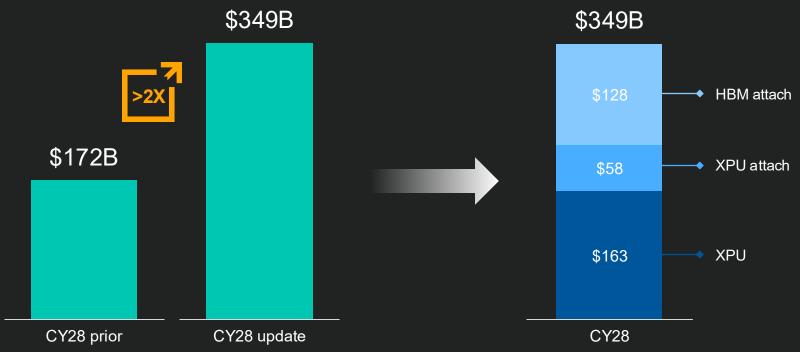

### Marvell<sup>®</sup> data center TAM

Data center TAM: Al Day April 2024

Source: 650 Group, CignalAI, Dell'Oro, LightCounting, and Marvell estimates

### Marvell data center TAM

Compute is 29% larger, interconnect is 37% larger

### Marvell data center TAM

Source: 650 Group, CignalAI, Dell'Oro, LightCounting, and Marvell estimates

### Marvell data center TAM

Source: 650 Group, CignalAI, Dell'Oro, LightCounting, and Marvell estimates

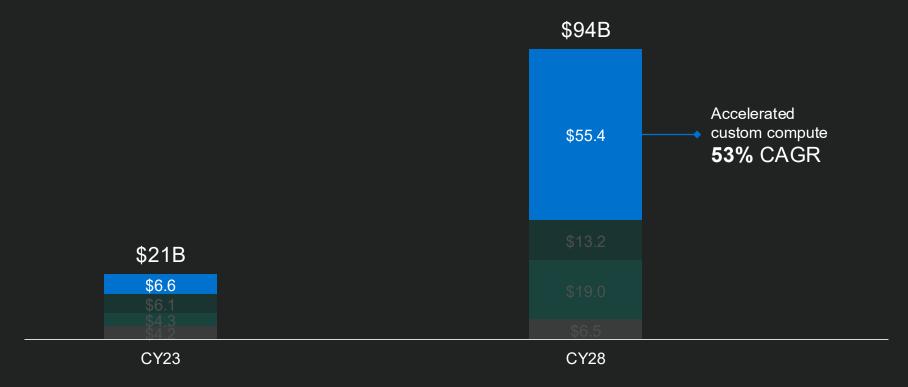

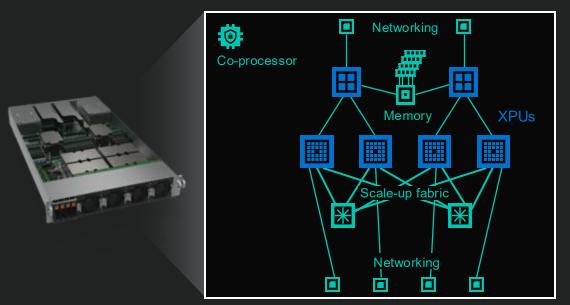

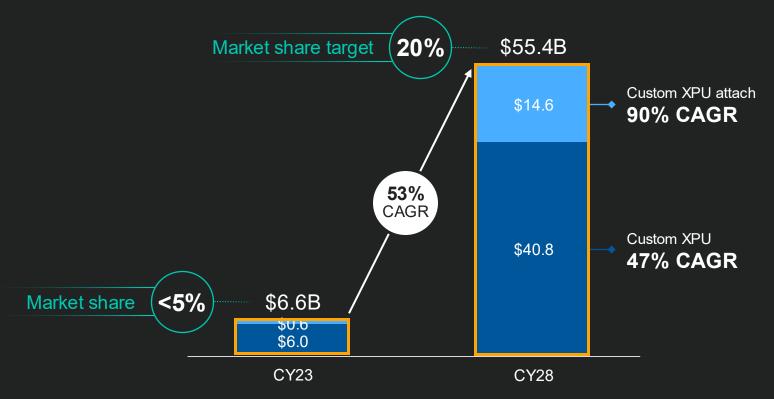

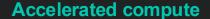

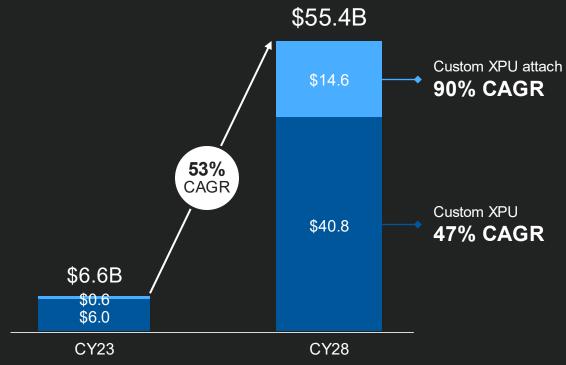

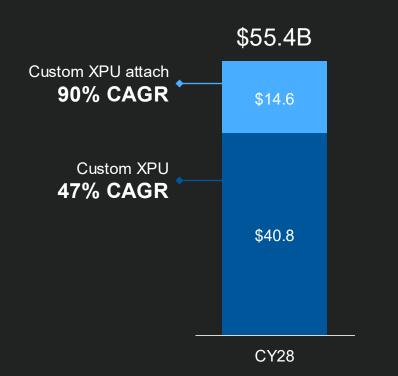

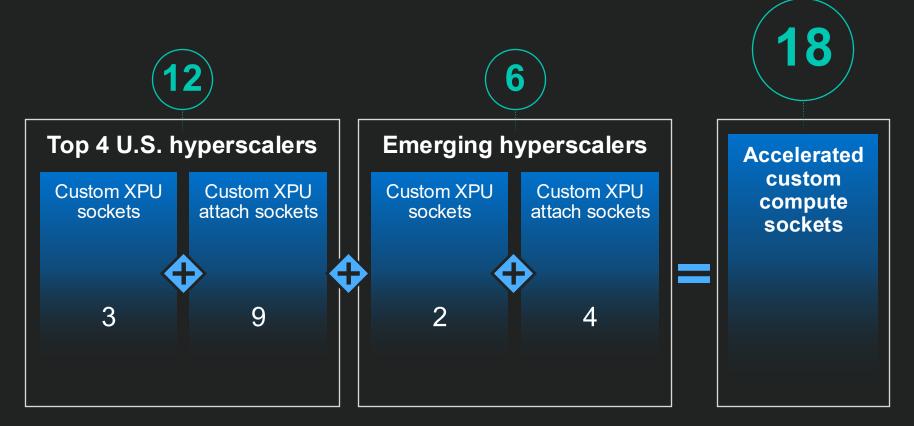

### Accelerated custom compute TAM = XPU

**Custom XPU**

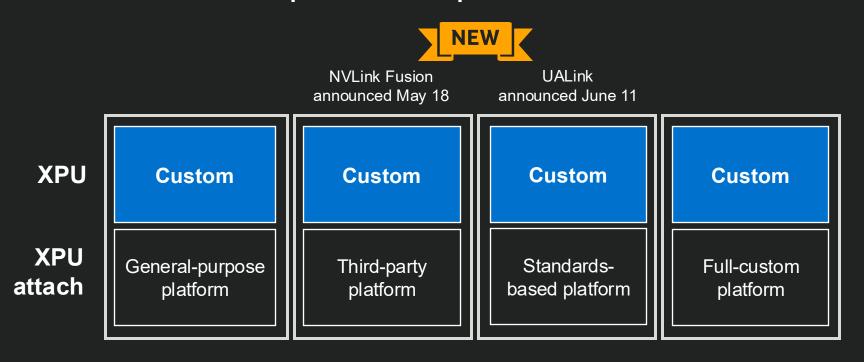

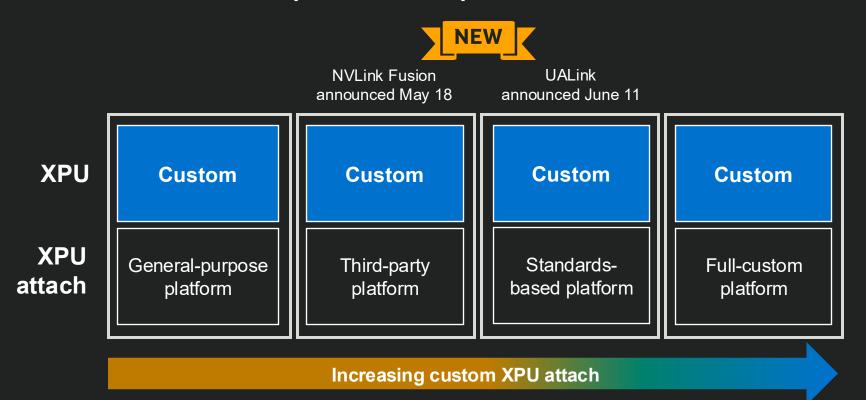

### **Expanding opportunity with custom XPU attach**

### Accelerated custom compute TAM = XPU + XPU attach

#### **Custom XPU**

#### **Custom XPU attach**

Network interfaces, scale-up fabrics, security and host management co-processors, memory poolers and expanders, etc.

### **Expanding opportunity with custom XPU attach**

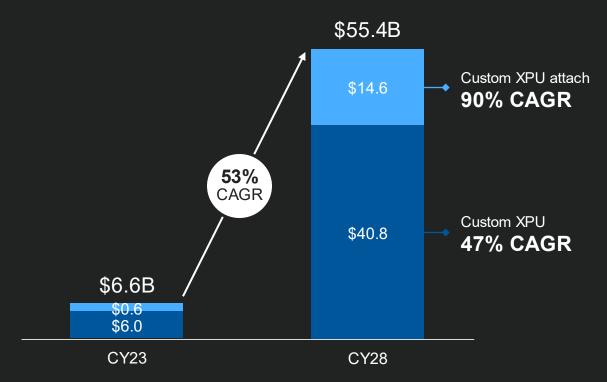

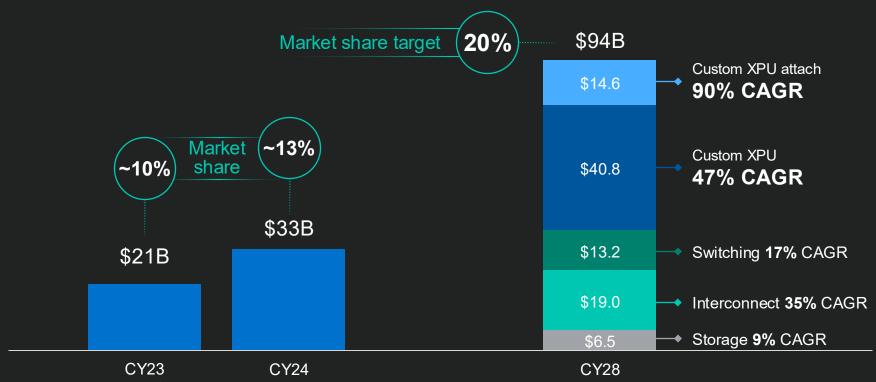

### XPU attach becoming increasing portion of custom TAM

Source: 650 Group, Dell'Oro, and Marvell estimates

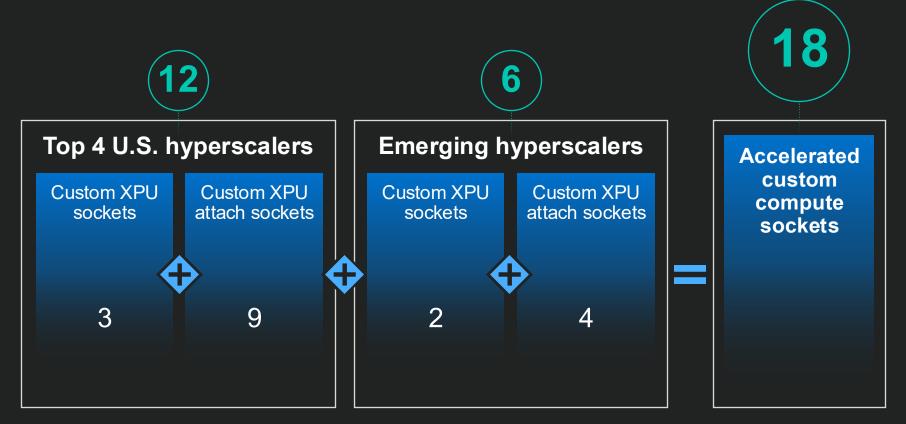

### Expanding multi-generational relationships

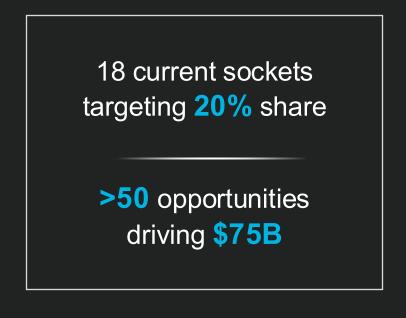

### Custom opportunity explosion

#### **Opportunities**

1/3 custom XPU 2/3 custom XPU attach

#### **Each XPU**

Multi-\$B lifetime 18 - 24 months

#### Each XPU attach

Several-\$100M lifetime 2 - 4 years

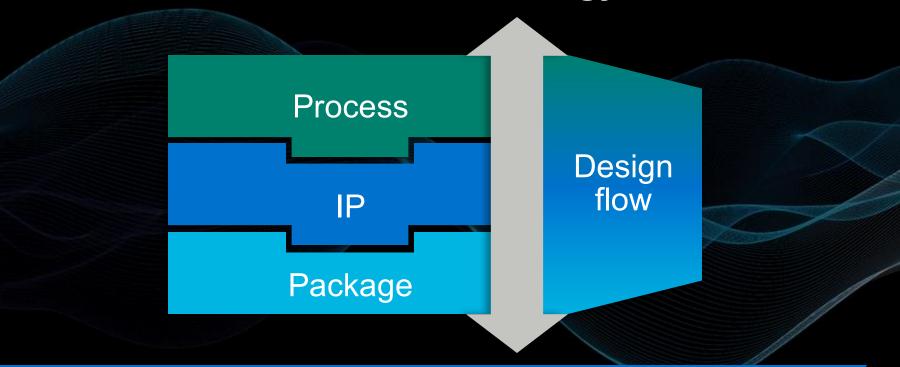

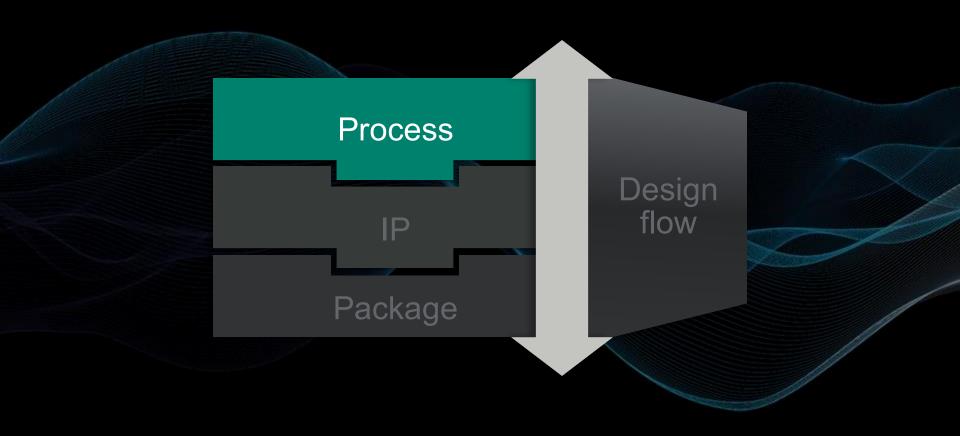

### Why we win: differentiating with full-service custom

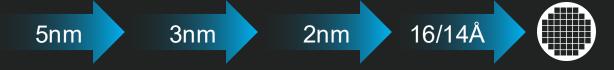

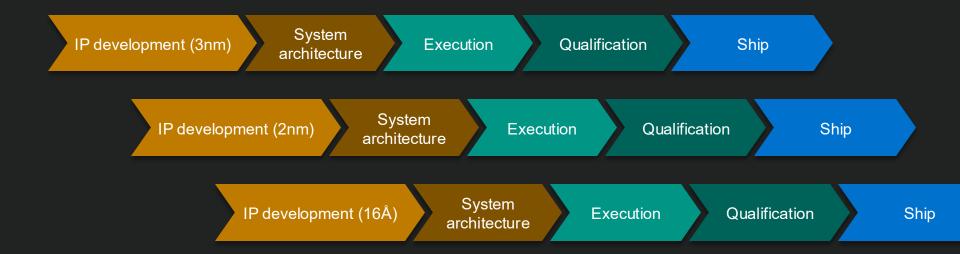

### Leading-edge technology drives multi-gen wins

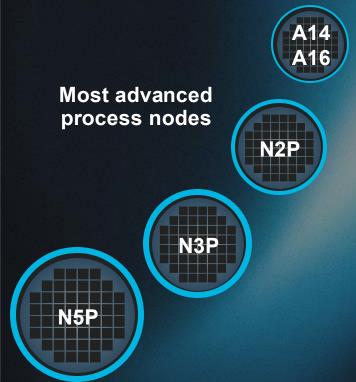

# **Process** 2nm **16Å** 14Å **Nanometers** to angstroms

EDA in the cloud

Custom and networking silicon

#### EDA in the cloud

# Custom and networking silicon

Building a cost and power efficient cloud at the scale that only AWS can deliver begins with leading-edge semiconductors designed to meet the demanding infrastructure needs of our customers. Our expanded collaboration with Marvell enables us to deploy our comprehensive semiconductor portfolio and specialized networking hardware to advance our mission to provide the industry's most robust and scalable cloud and AI services to our customers.

**Matt Garman, CEO at AWS**

### Rani Borkar

Corporate Vice President, Azure Hardware Systems and Infrastructure, Microsoft

Video content

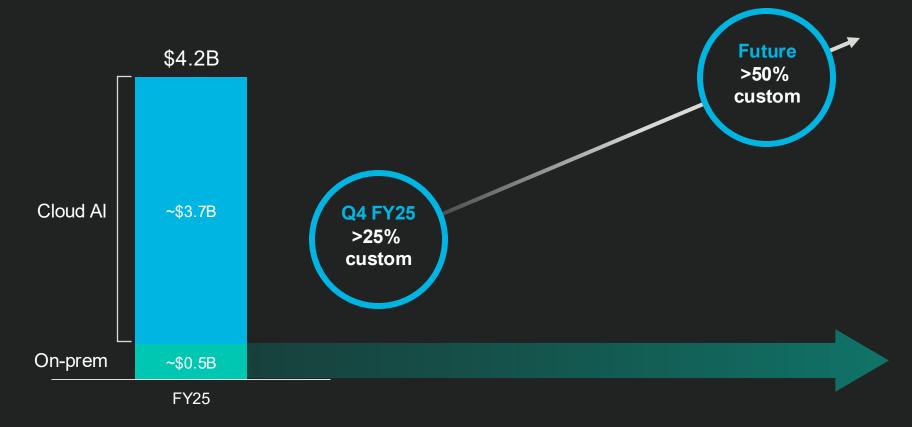

### Marvell's data center revenue

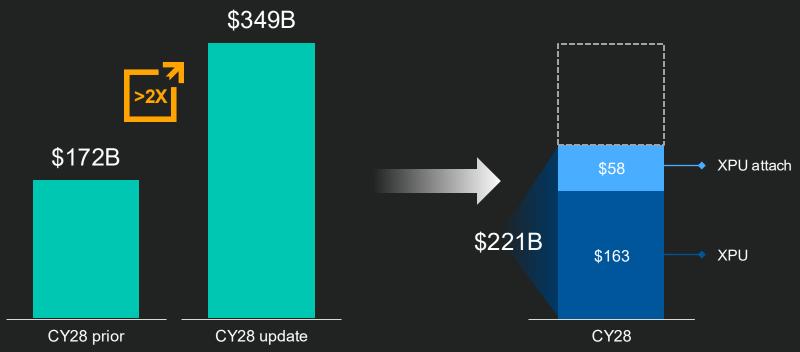

### Driving to 20% share in custom compute and attach

Source: 650 Group, Dell'Oro, and Marvell estimates

### On track for 20% share in overall data center

Source: 650 Group, CignalAI, Dell'Oro, LightCounting, and Marvell estimates

### On track for 20% share in **overall data center**

Market share based on Marvell fiscal year Source: 650 Group, CignalAI, Dell'Oro, LightCounting, and Marvell estimates

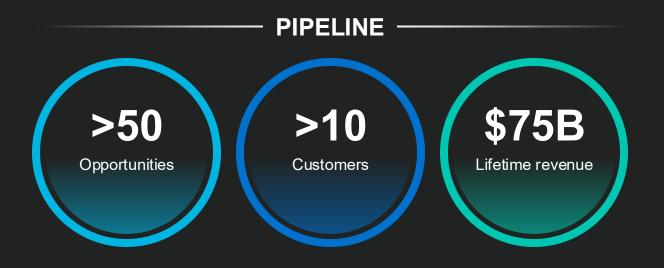

\$75B >> \$94B Larger TAM Custom XPU

Custom XPU attach New markets ~10% ~ ~13% ... 20% Increasing share More sockets won >10 More customers

>50 opportunities

\$75B

# **Custom Al Investor Event**

# Chris Koopmans

**Chief Operating Officer**

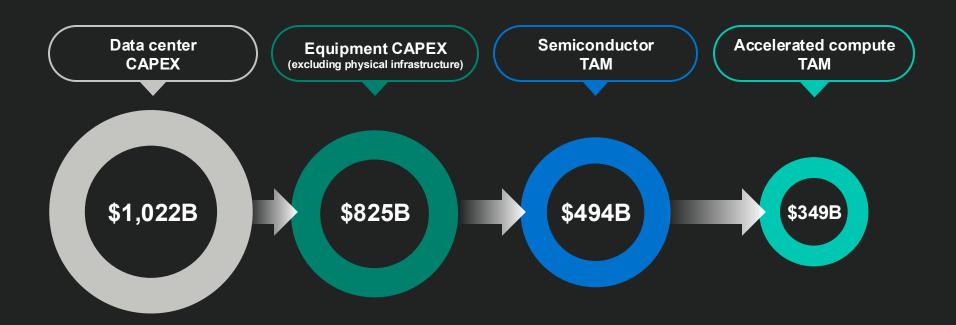

#### 2028 data center infrastructure market

Source: 650 Group, CignalAI, Dell'Oro, LightCounting, and Marvell estimates

#### Breaking down accelerated computing TAM

Source: 650 Group, Dell'Oro, and Marvell estimates

#### Breaking down accelerated computing TAM

Source: 650 Group, Dell'Oro, and Marvell estimates

#### Custom silicon on track for 25% share of market by 2028

Source: 650 Group, Dell'Oro, and Marvell estimates

#### Marvell custom silicon TAM

#### **Marvell TAM**

Source: 650 Group, Dell'Oro, and Marvell estimates

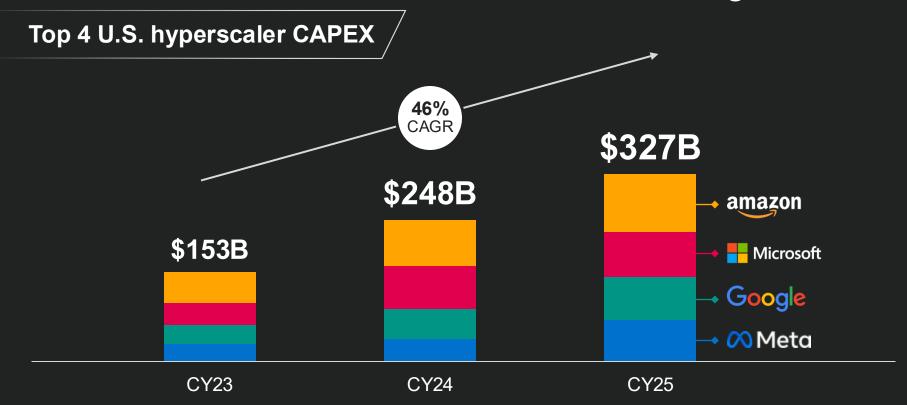

#### Diversity drives specialization,

which drives customization

Race to the million-XPU cluster speeding up

Microsoft 14K

XPUs **2023**

Meta

100K

XPUs

2024

xAI 200K XPUs 2025 1M XPUs

Microsoft

10K

XPUs **2020**

#### **Model innovation continues**

#### Large language model

Content writing

Live chatbots

Search — — Analyze← → Conclude

#### Reasoning model

Code writing

Complex math

Puzzle solving

#### Rise of inference-optimized infrastructure

# One size does not fit all

Training

Chain of thought inference

Inference

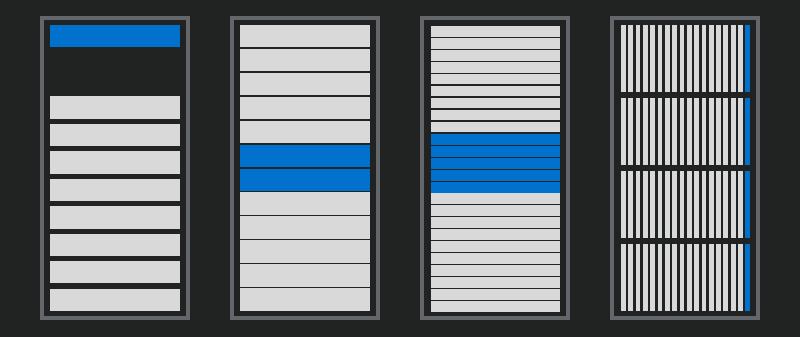

#### As Al workloads diversify, so must the infrastructure

#### Diversification creates more opportunities

#### Specialization drives diversity of compute core design

#### **Multiple points of optimization**

Core architectures

# cores

Level of precision

Ratio of cores to memory

#### Programmable, powerful, purpose-built

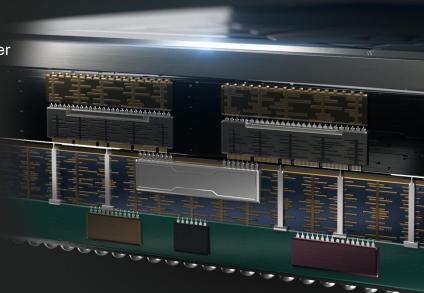

#### And diversity of memory, packaging, connectivity

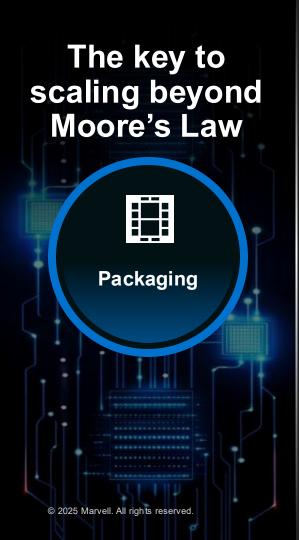

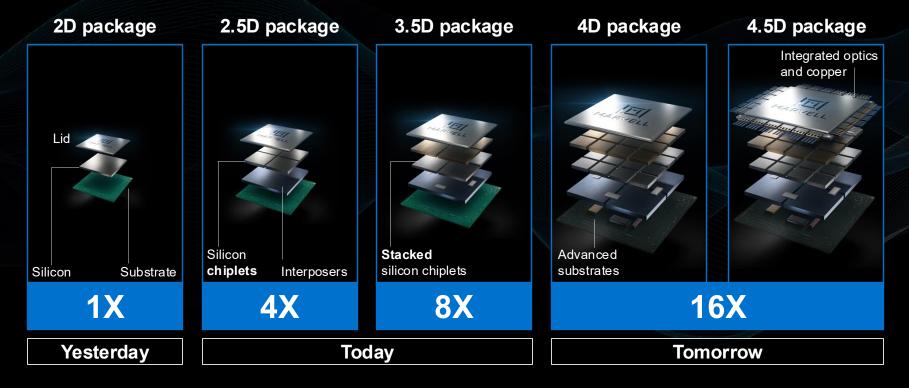

Beyond one chip, advanced packaging powers scale

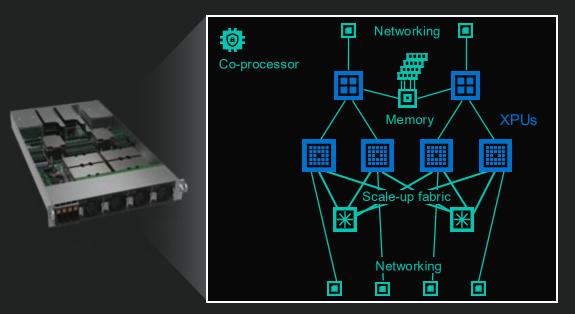

#### And diversity of the entire scaled-up platform design

#### **Optimized infrastructure for specific workloads**

#### Al infrastructure platform options

#### Al infrastructure platform options

#### Growing TAM supports further pipeline expansion

Source: 650 Group, Dell'Oro, and Marvell estimates

## **Custom Al Investor Event**

## Nick Kucharewski

SVP and GM, Cloud Platform

#### Marvell Custom Cloud Solutions

30 years of experience

First-time-right silicon design

Comprehensive portfolio

Silicon-proven core enabling IP

Full-lifecycle partnership

Definition through deployment

# Choosing a custom silicon partner

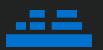

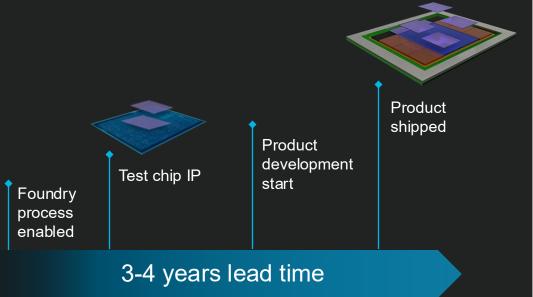

#### Pace of innovation in Al cloud infrastructure

New key enabling technologies every year

... applications demand system innovation every < 2 years

... a 1-day delay means millions \$ in lost revenue

Physical design services

Manufacturing

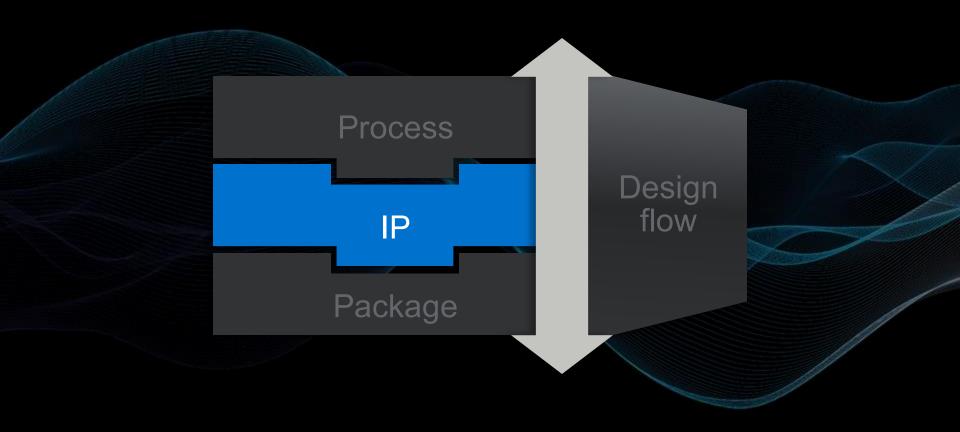

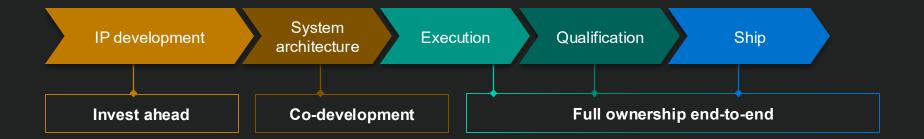

# Marvell: Full-Lifecycle Custom Cloud

Unique differentiated technology, not available on the open market

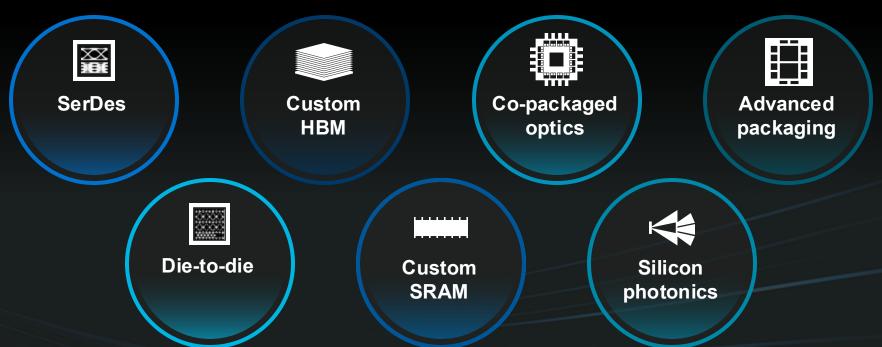

#### New technology development

Incubation 2-4 years before project start

#### **Evaluation and assessment**

Concept systems enable customer exploration

#### **Cooperative system definition**

Iterate on power, performance, cost tradeoffs

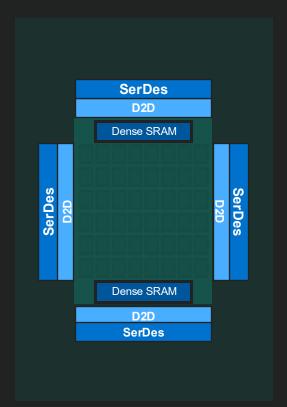

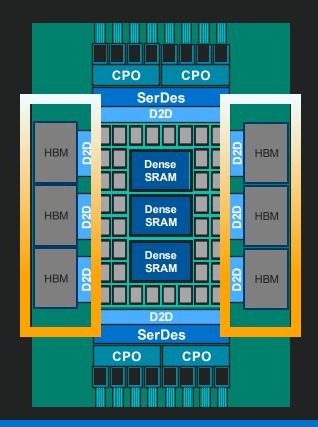

#### Key enabling core tech

SerDes

Die-to-die

Compute cores

Compute fabric

Marvell

Multi-die

Security

Ethernet MAC

**Packet** fabric

Specialized SW/FW

Compress / decompress

Custom HBM

Dense SRAM

Hardened Arm

**Ecosystem**

arm

cadence

SYNOPSYS°

Start-ups

# Running ahead of the customer project

#### **Process enablement**

IP migration

Test silicon

Model creation

EDA toolflow

#### **Design execution**

Logic design

Physical design

DFT and DFM

Power tuning

Yield enhancement

#### Multi-die

Marvell custom and TSMC CoWoS

#### **HBM**

Marvell custom and JEDEC

### Advanced substrate

Leadership roadmap

**CPC**

Co-packaged copper

**CPO**

Co-packaged optics

#### Scale

Leading fabless manufacturer

#### Quality

Billions of device-hours over multiple decades

#### Readiness

Operations engineering for volume delivery

Product engineering

Test engineering

Quality assurance

Reliability assessment

Physical design services

Manufacturing

#### Running faster and faster

Leading systems need access to the leading tech, every generation

# Marvell Full-Lifecycle Custom Cloud

- ✓ Partnership for system design

- **Exclusive** enabling technology

- **Experience** at volume scale

## **Custom Al Investor Event**

## Sandeep Bharathi

**Chief Development Officer**

Ken Chang

SVP, Analog and Mixed Signal Engineering

Mark Kuemerle

VP, Technology, Custom Cloud Solutions

Radha Nagarajan

SVP and CTO, Optical Engineering

Mayank Mayukh

Senior Distinguished Engineer, Advanced Packaging Al compute cycle accelerates

Al compute doubling less than a year

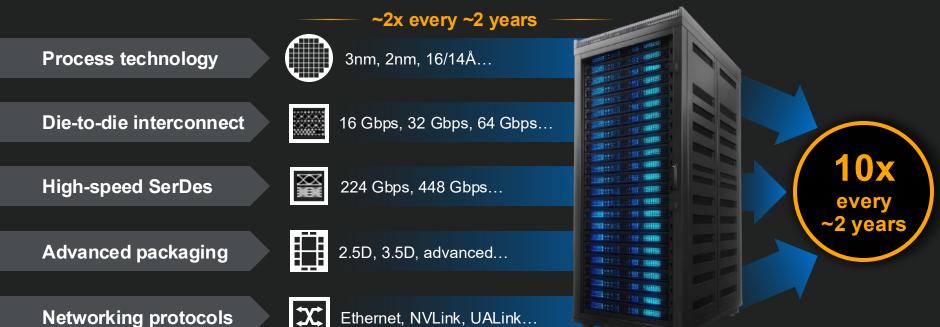

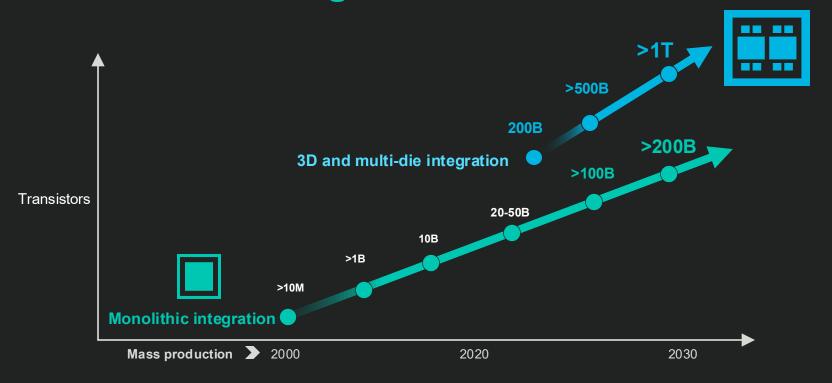

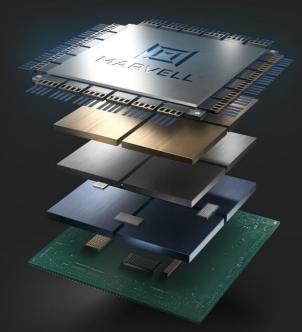

#### Al accelerates single-die to multi-die transition

#### Al accelerates single-die to multi-die transition

#### Trillion+ transistors requires rack-scale integration

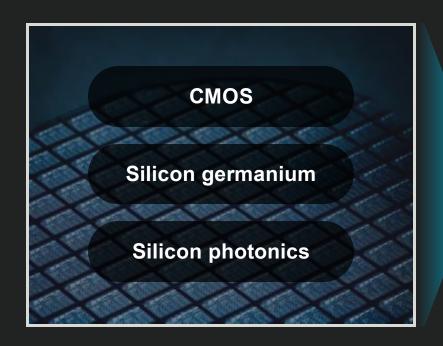

#### Proven Marvell technology stack

Multi-generational execution track record

#### Process technology leadership

Validated critical IP ahead of product development

#### Marvell IP across process technologies

#### Process-agnostic. Foundry-ready. Future-proof.

#### Industry-leading customized IP portfolio

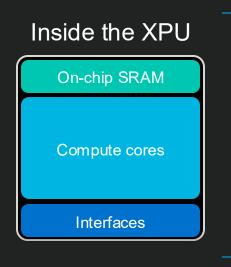

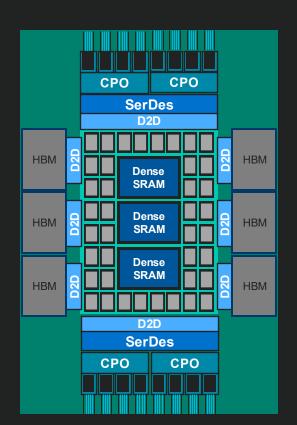

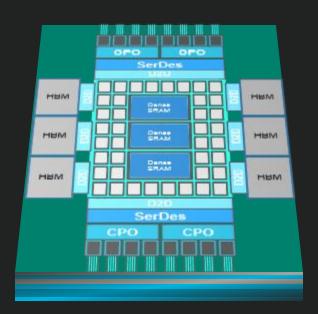

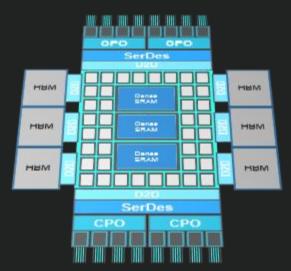

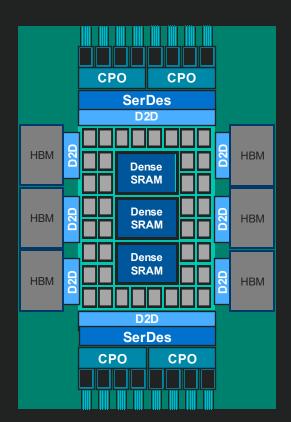

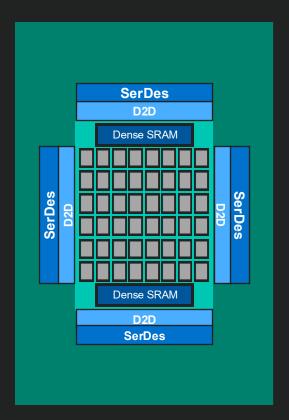

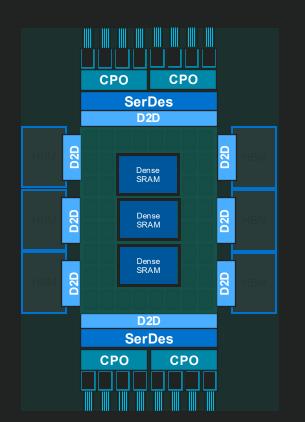

# Anatomy of a modern

# Anatomy of a modern

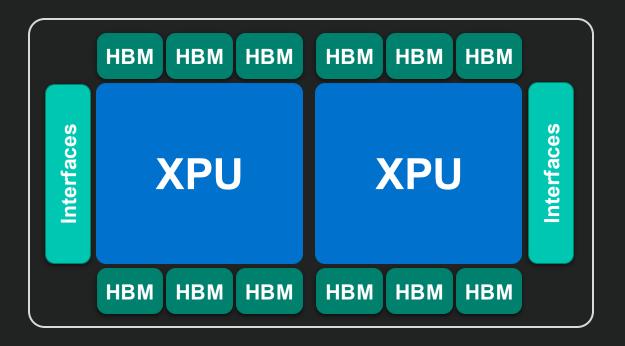

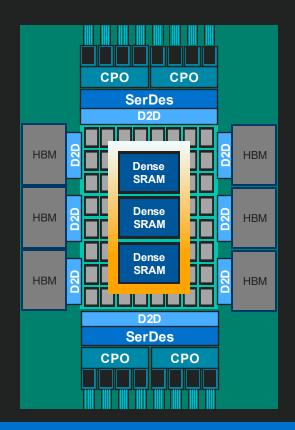

# Modern **XPU** and **XPU** attach © 2025 Marvell. All rights reserved.

# Modern XPU and XPU attach

Customization to achieve the highest performance per watt

#### Figures of merit

Reach

Power

Latency

Bit error rate

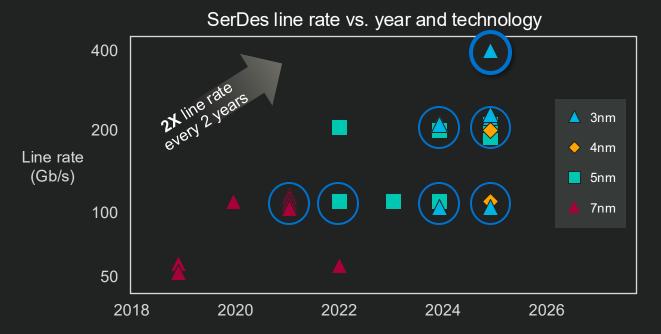

Marvell has multi-generational SerDes leadership

#### Marvell IP leadership

#### Focused investment enables first-to-market advantage

## **Custom Al Investor Event**

# Ken Chang

SVP, Analog and Mixed Signal Engineering

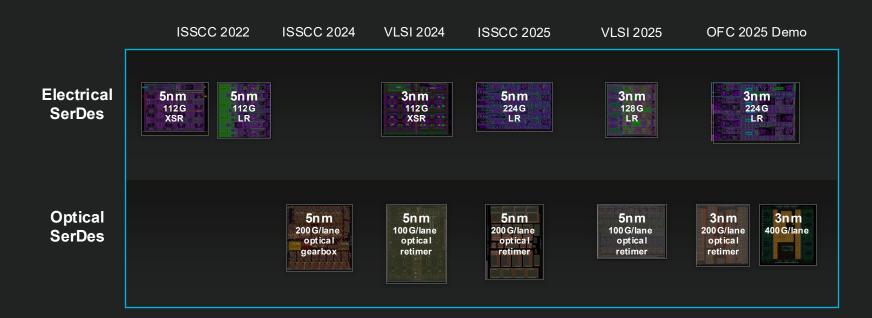

#### Marvell SerDes leadership in IEEE spotlight

#### Key leadership metrics

**Lowest** power

Highest reach

**Lowest BER**

Lowest area

#### Marvell SerDes recognized by IEEE

Source: ISSCC, VLSI, OFC, industry SerDes papers

#### Marvell SerDes leadership in IEEE spotlight

#### **Enabling next-generation XPU platforms**

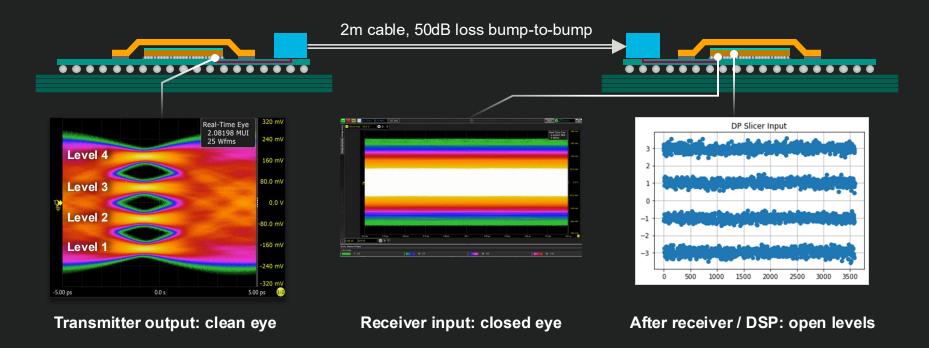

#### Marvell 3nm 224Gbps SerDes at OFC

#### **Enabling next-generation XPU platforms**

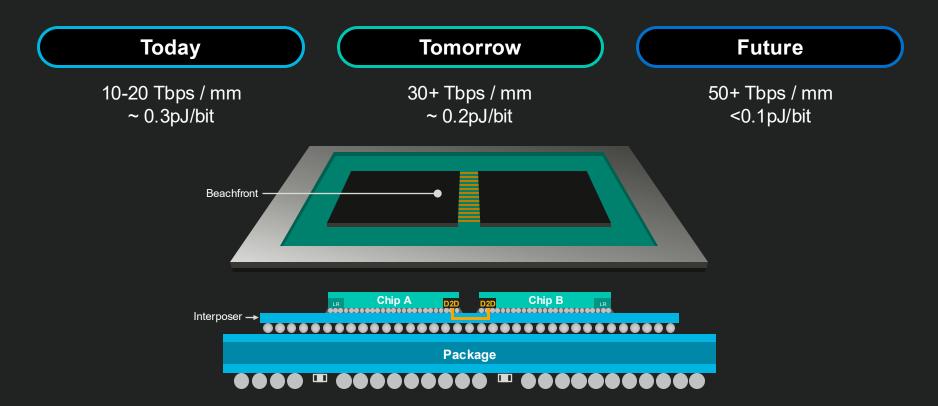

#### Marvell die-to-die (D2D)

## **Custom Al Investor Event**

## Mark Kuemerle

VP, Technology, Custom Cloud Solutions

#### Custom dense SRAM

On-chip embedded SRAM – customization is key

#### Marvell custom SRAM

Key metrics for embedded memories

|                           | Marvell vs. industry |

|---------------------------|----------------------|

| Area at same bandwidth    | 50% lower            |

| Standby<br>power          | 66% lower            |

| Bandwidth<br>at same area | 17x higher           |

#### Bandwidth / mm<sup>2</sup> of memory options

Comparison of 1 Mb instance of third-party dense memories vs. Marvell Marvell IP provides 17x bandwidth-density improvement

#### **Custom HBM**

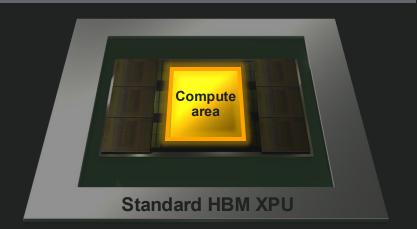

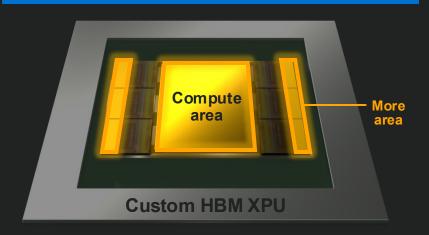

**Custom HBM – high capacity with minimal overhead**

#### Enhancing XPUs with custom HBM architecture

### Standard HBM No chiplets

- 1X useful compute area

- No compute area on HBM

- 1X power

### Marvell Custom HBM With I/O chiplets

- 1.7X useful compute area

- More compute area on HBM

- **75% lower** memory I/O power

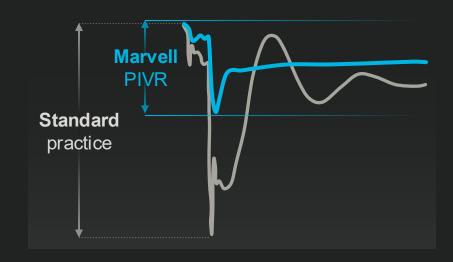

#### Package-integrated voltage regulation (PIVR)

85% lower IR power

15% lower total product power

#### 60% lower power noise

## **Custom Al Investor Event**

## Radha Nagarajan

SVP and CTO, Optical Engineering

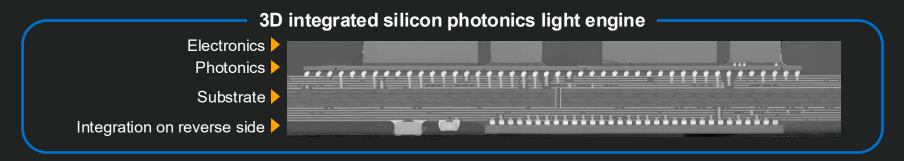

#### Silicon photonics is critical for co-packaged optics

- Optical system-on-chip

- High speed, long reach

- High volume CMOS fabs

- Complex electronics and photonics integration

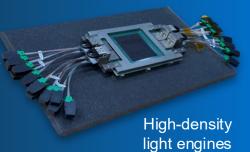

#### Highly integrated light engines for all interconnects

#### Marvell silicon photonics at scale

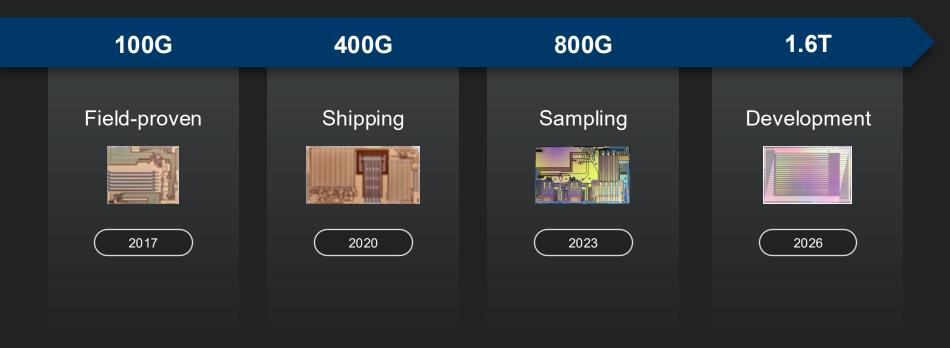

#### Multiple generations of field-deployed silicon photonics

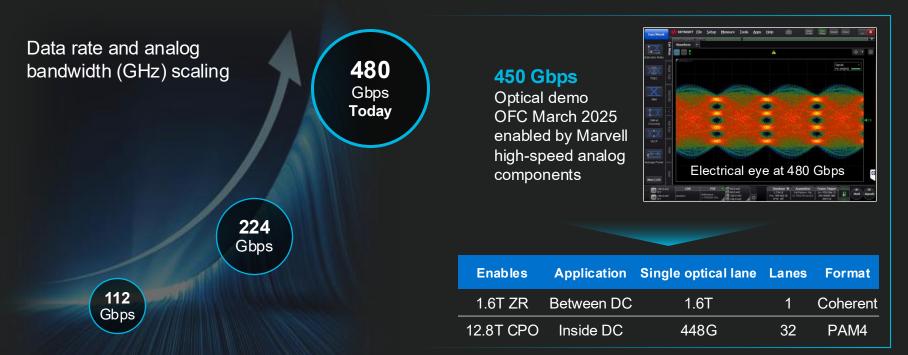

#### Marvell breaking 500 Gbps data rate barrier

#### 2X analog bandwidth every 2 years

#### Co-packaged optics to custom silicon interconnect

**6.4T** per engine

32 x 224G optical lanes

**25.6T** 4 engines

Custom silicon interconnect

Marvell high-density custom silicon interconnects for Al

## **Custom Al Investor Event**

## Mayank Mayukh

Senior Distinguished Engineer, Advanced Packaging

#### Marvell advanced packaging strategy

Robust ecosystem for faster cadence between custom packaging generations

**Proprietary** technology

Materials, process, design

**Fungible** building blocks

Scaling, optics, copper, components

Generational portfolio

Long-range roadmap for building blocks

Custom packaging solution

#### Marvell advanced packaging portfolio

Road to packaging a trillion transistors together

#### Marvell advanced packaging toolbox

Fungible toolbox for generational portfolio

Integrated optics and copper

3D-stacked silicon chiplets

Bridge or RDL interposer

Advanced substrates

# Will Chu

SVP and GM, Custom Cloud Solutions

Compute

**ASIC**

#### Strong design win momentum

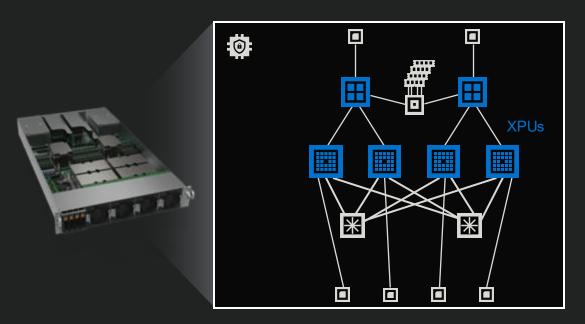

#### Typical system architecture

## Providing unique customer value: typical XPU

Rack-scale enablement and optimization

Critical IPs

Arm

Die-to-die Dense SRAM

Design-to-spec and co-development

Marvell custom and TSMC CoWoS

Faster time to market

## Providing unique customer value: typical XPU attach

Production FW/SW, boards, and ecosystem

Critical IPs

Compress / Compute decompress fabric

Security

SerDes

Design-to-spec integrating customer IP

#### Unique value across a single complete program

#### Unmatched combination of technology, expertise and scale

## Unique value driving multi-generational partnerships

#### Concurrent engagement enables a new chip every year

#### Investing ahead in breakthrough technologies

Marvell Introduces Optimized

Integrated Power Solutions

to Boost Performance, Efficiency,

and ROI of Accelerated Infrastructure

June 17, 2025

Marvell Delivers Advanced Packaging Platform for Custom Al Accelerators

May 9, 2025

Marvell Announces Breakthrough

Co-Packaged Optics Architecture

for Custom Al Accelerators

January 6, 2025

Marvell Develops Industry's First 2nm

Custom SRAM for Next-Generation

Al Infrastructure Silicon

June 17, 2025

Marvell Demonstrates

Industry's Leading 2nm Silicon

for Accelerated Infrastructure

March 3, 2025

Marvell Announces Breakthrough

Custom HBM Compute Architecture

to Optimize Cloud Al Accelerators

December 10, 2024

#### Rapidly expanding pipeline

Engaged in every opportunity and well-positioned for growth

# Thank you

June 17, 2025